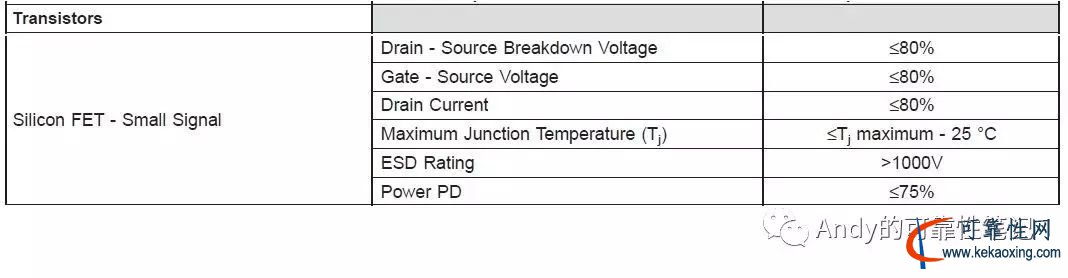

上篇分享了双极型三极管(Bipolar Junction Transistor)的降额案例,这篇继续分享下常用的场效应管(MOSFET)的降额分析,依旧采用IPC9592的降额规范,截图如下。

上篇分享了双极型三极管(Bipolar Junction Transistor)的降额案例,这篇继续分享下常用的场效应管(MOSFET)的降额分析,依旧采用IPC9592的降额规范,截图如下。

注意:发现IPC9592已经更新到了2012版本,之前用的一直是2007年的版本做的降额示例,今天开始更新下。

由图可知,降额要求如下:

1) 击穿电压VDS(Drain-Source Breakdown Voltage)≦80%;

2) 栅源电压VGS(Gate-Source Voltage)≦80%;

3)漏源电流ID(Drain Current)≦80%;

4) 最大结温(Maximum Junction Temperature)≦Tjmax-25°C

5) ESD Rating >1000V;

≦

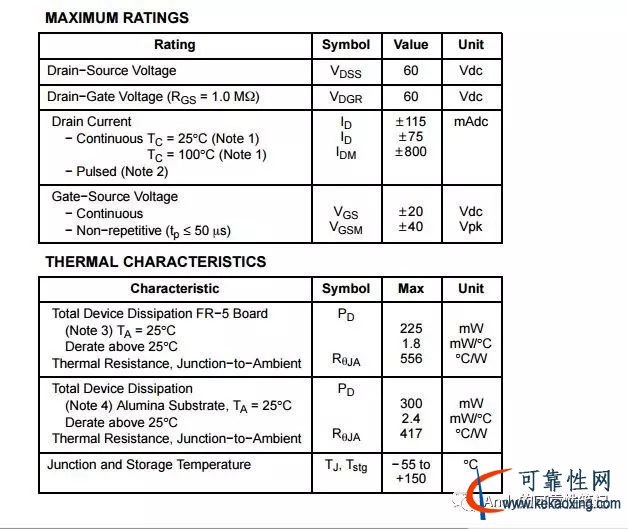

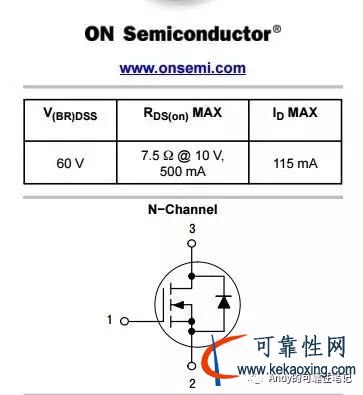

选取一颗小信号MOSFET (2N7002LT1G),截取Datasheet如下图,得出如下降额有用信息(如下均为25度下额定值):

1)击穿电压VDS=60V;允许降额为:60*80%=48V;

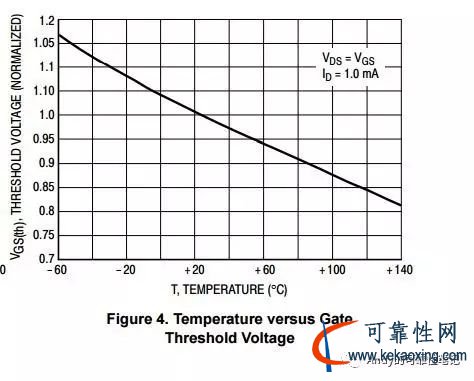

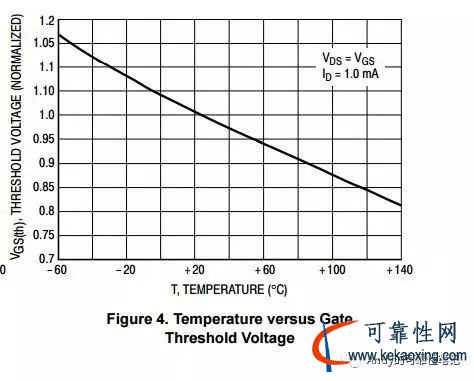

2) 栅源电压VGS=20V; 与温度也有关系,下面第三张图,例如60度时,额定Vgs约为0.94*20=18.8V;则60度时允许降额为:18.8*80%=15.04V;

3) 漏源电流ID=115mA; 允许降额为:115*80%=92mA;

4) 最大结温(Tj)=150°C;允许降额为:150-25=125°C

5) ESD Rating :Datasheet 无此数据,需要询问供应商。1000V;

6)功耗(Power)=225mW@25°C,25度以上降额为1.8mW°C(这次对应选择FR-5一种常用的基材,具体情况具体分析);假设该场效应管的工作环境温度为60°C,则60度下额定功率为:225-(60-25)*1.8=162mW; 60度下允许降额为:162*75%=121.5mW;

注意:这里记录下RθjA=556°C/W(见下第一张图),下面计算结温会用到;

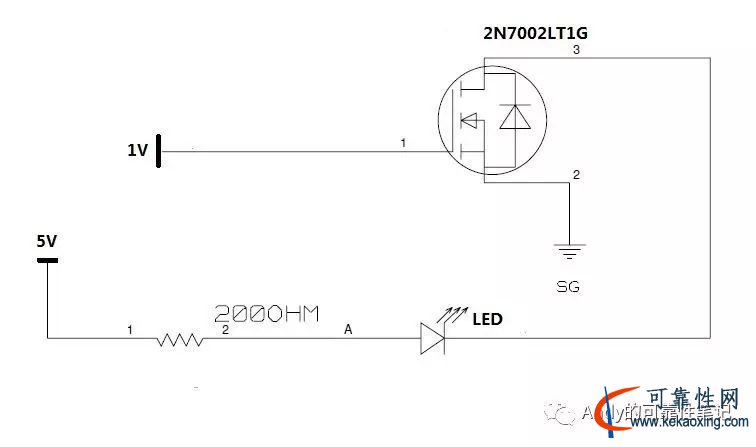

举下面一则工作中碰到的电路如下进行电路降额分析,由下图可知,实际Vgs=1.0V(小于允许降额48V);

Vds=5V-200欧姆电阻分压-LED分压——–公式1

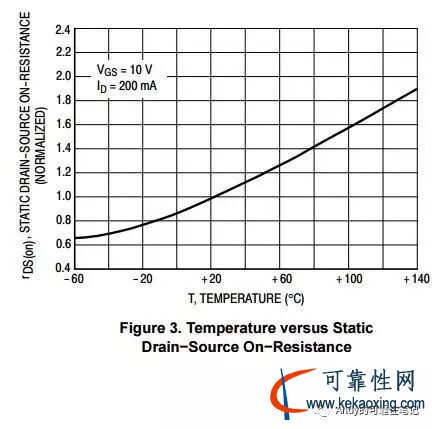

注意:这里需要计算实际Ids电流,需要知道导通电阻Rds(on)的大小,由Datasheet可知,Rds(on)=7.5欧姆;见下面第二张图;而Rds和Vgs以及自身Id以及温度都有关系,例如当Vgs=10V,Id=200mA时,温度为60度时,Rdson约为原来的1.25倍,为1.25*7.5=9.375欧姆;见下面第三张图。

关于公式1的计算,采用简单评估法,LED通常开启电压为1.7V,200欧电阻分压为:(5-1.7)V/(200+9.375)ohm*200ohm=3.15V;则

Vds=5-3.15-1.7=0.15V;

Ids=(5-1.7)/(200+9.375)=15.76mA,

P=Vds*Ids=0.15*15.76=2.36mW;

综上所述,实际应用中参数:

Vgs=1.0V(小于允许降额15.04V)

Vds=0.15V(小于允许降额48V)

Ids=15.76mA(小于允许降额92mA)

P=2.36mW(小于允许降额121.5mW)

Tj=TA+RθjA*P=60°C+556°C/W*2.36*0.001=61.31°C(小于允许降额125°C)

如上,为个人笔记,欢迎交流,如有错误和不同的意见还请指出,谢谢~~